SEMI

Post Dicing

Post Dicing为晶圆完成切割后,针对单颗晶粒(Die)进行检测的步骤,主要目的在于确保切割品质与晶粒完整性,避免缺陷进入后续封装与先进封装制程。随着 Fan-out、2.5D/3D IC、HBM等应用日益普及,对单颗晶粒品质的要求持续提高,使 Post Dicing 检测成为影响整体良率与可靠度的重要环节。在 Post Dicing 制程中,切割应力可能导致晶粒边缘崩裂、微裂纹也有切割偏移及残留缺陷等问题,部分缺陷甚至不易察觉,若未及时检出,将对后续制程对位、堆叠与长期可靠度造成风险。

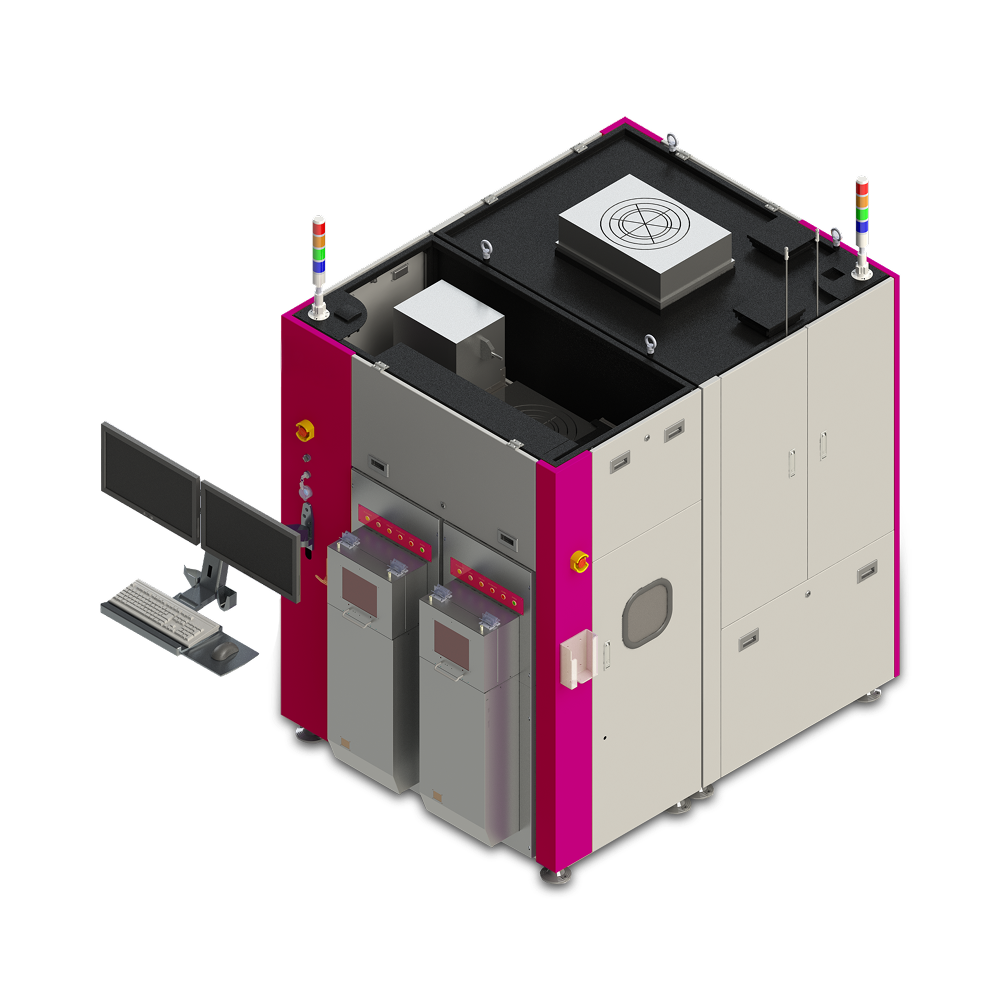

政美应用(CMIt)针对晶粒侧壁裂纹开发专用检测技术,可于早期制程阶段识别潜在关键缺陷。系统支援多种工件型态(workpieces)与尺寸配置,具备高度制程弹性,可满足不同制程阶段与量产环境需求。